12月5日消息,晶体管这个概念想必大家都有所了解,它属于微型电子开关的一种,堪称计算机芯片运行的基础所在。

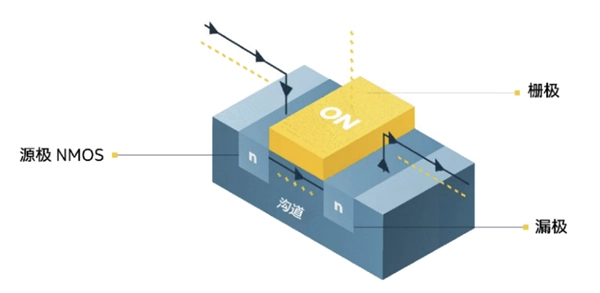

典型的晶体管主要由三部分组成:

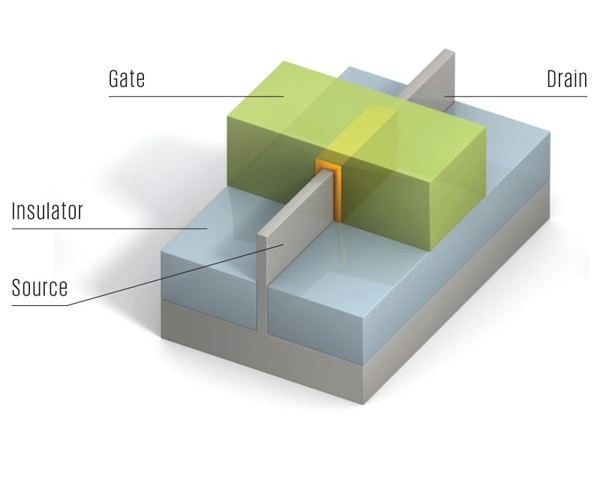

-栅极(gate):相当于开关的把手,通过施加电压实现对电流的控制。

-沟道(channel):指的是电流的通道。

-源极(source)和漏极(drain):分别是电流的入口和出口。

而晶体管架构,指的是设计晶体管的方式,主要是栅极、沟道、源极、漏极的几何布局。

再引入另一个名词,MOSFET,全名金属氧化物半导体场效应晶体管,是目前数字电路中主流的晶体管架构。

在MOSFET晶体管中,栅极和沟道之间被氧化层(oxide layer)完全隔离开来。

一方面,氧化层阻止了电流直接从栅极流向沟道,强化了对电流的控制,避免漏电。

另一方面,当施加电压时,由于电容效应,栅极上的电荷会在氧化层下方产生一个电场,“间接”驱动晶体管中的电流流动。

在以前,制造氧化层的主要材料是二氧化硅。

2007年,Intel在业界率先将高K材料应用于45纳米工艺的商业化产品中,这一技术即HKMG(高K金属栅极)。它有效增大了栅极电容,同时优化了漏电问题,从而推动了晶体管性能的提升。

这里的“K”指的是介电常数,即衡量一种绝缘材料在电场中储存电能能力的比例系数。

除了MOSFET之外,还存在多种其他类型的晶体管架构,像BJT(双极性结型晶体管)、HEMT(高电子迁移率晶体管)以及MESFET(金属半导体场效应晶体管)等都属于这一范畴。

MOSFET是数字电路的主流,而其他架构的产品主要应用于射频电路、功率电子、高速模拟等特定领域。

传统的MOSFET架构都是平面型,所有组件都在一个水平面上,栅极只能覆盖沟道顶部。

这就产生了短沟道效应(SCE),具体是指当晶体管的沟道长度变得极短时,除栅极电场之外,源极与漏极的电场对沟道的作用会随之增强,从而引发阈值电压降低、反偏效应加剧等情况,进一步造成漏电以及性能波动等问题。

随着晶体管尺寸越来越小,平面MOSFET中的短沟道效应已经无法克服。

2010年代初期,Intel 22nm工艺上率先实现了FinFET晶体管架构的商业化。

FinFET晶体管中,沟道水平排列,栅极三面环绕,看起来很像鱼鳍,因此叫作“鳍式场效应晶体管”。

FinFET借助增强栅极对沟道的“包裹”作用,在芯片制程从20多纳米微缩至3纳米的进程里,成功应对了性能与功耗等领域的挑战。

如今,随着工艺制程迈向2nm级别,FinFET在控制短沟道效应和提升性能方面也捉襟见肘。

为此,产业界纷纷转向控制能力更强的全环绕栅极(GAA)架构,例如Intel 18A工艺中首次应用的RibbonFET技术。

RibbonFET采用垂直堆叠沟道的设计,栅极以“四面环绕”的方式将沟道完全包裹,这样一来,栅极对电流的控制能力得以增强,同时控制效果更稳定、更均匀,也更不容易受到源极与漏极电压波动的影响。

另一方面,当沟道宽度变大时,晶体管的导电能力会增强,能够驱动更强的电流。

在FinFET里,若想加宽沟道,就得把晶体管做得更高;但对于RibbonFET而言,由于沟道呈水平形态,在特定范围内,加宽沟道并不需要增大晶体管的体积。

换言之,RibbonFET架构的晶体管,能够用更小的体积实现相同的性能。

在芯片层面,这就意味着芯片标准单元的高度会降低、面积会缩小,这样一来,相同空间里就能容纳更多晶体管,进而推动设备整体性能的提升。

Intel 18A工艺还有PowerVia背部供电技术,已经投入量产,首款产品Panther Lake即将发布!